Page 20 - 156-PENERAPAN_RANGKAIAN_ELEKTRONIKA

P. 20

PENERAPAN RANGKAIAN

ELEKTRONIKA

MATERI PEMBELAJARAN

b. Jumlah gerbang AND (Kondisi)

c. Jumlah gerbang OR (sebagai modul keluaran)

Gerbang logika yang digunakan tidak mengubah konfigurasinya,

sedangkan satu-satunya matriks yang berubah adalah tautan yang dapat

dikonfigurasi. Matriks penghubung bertindak seperti sekering. Variasi

arsitektur PLA yang hanya mengubah (mengaktifkan) lokasi gerbang AND dan

OR yang dapat dikonfigurasi adalah Programmable Array Logic (PAL).

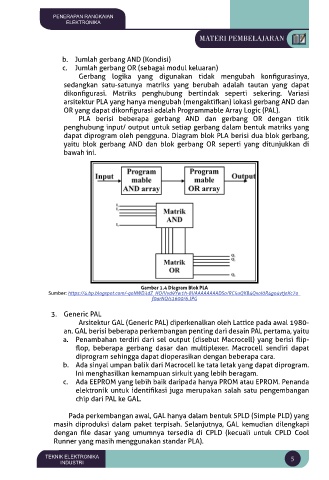

PLA berisi beberapa gerbang AND dan gerbang OR dengan titik

penghubung input/ output untuk setiap gerbang dalam bentuk matriks yang

dapat diprogram oleh pengguna. Diagram blok PLA berisi dua blok gerbang,

yaitu blok gerbang AND dan blok gerbang OR seperti yang ditunjukkan di

bawah ini.

Gambar 1.4 Diagram Blok PLA

Sumber: https://4.bp.blogspot.com/-qoNWD3dZ_HQ/Vvd9Yw1h-8I/AAAAAAAADSo/RC5uQKB4Qxoi0R4go4vtjeXc7o_

f0arNQ/s1600/6.JPG

3. Generic PAL

Arsitektur GAL (Generic PAL) diperkenalkan oleh Lattice pada awal 1980-

an. GAL berisi beberapa perkembangan penting dari desain PAL pertama, yaitu

a. Penambahan terdiri dari sel output (disebut Macrocell) yang berisi flip-

flop, beberapa gerbang dasar dan multiplexer. Macrocell sendiri dapat

diprogram sehingga dapat dioperasikan dengan beberapa cara.

b. Ada sinyal umpan balik dari Macrocell ke tata letak yang dapat diprogram.

Ini menghasilkan kemampuan sirkuit yang lebih beragam.

c. Ada EEPROM yang lebih baik daripada hanya PROM atau EPROM. Penanda

elektronik untuk identifikasi juga merupakan salah satu pengembangan

chip dari PAL ke GAL.

Pada perkembangan awal, GAL hanya dalam bentuk SPLD (Simple PLD) yang

masih diproduksi dalam paket terpisah. Selanjutnya, GAL kemudian dilengkapi

dengan file dasar yang umumnya tersedia di CPLD (kecuali untuk CPLD Cool

Runner yang masih menggunakan standar PLA).

TEKNIK ELEKTRONIKA 5

INDUSTRI