Page 23 - LFT Presentation Jan2021 49SA

P. 23

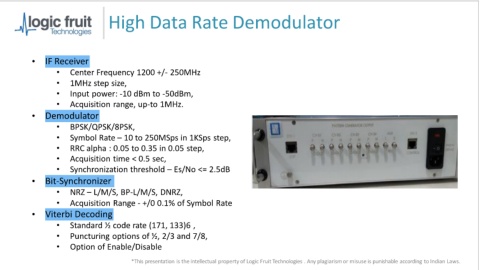

High Data Rate Demodulator

• IF Receiver

• Center Frequency 1200 +/- 250MHz

• 1MHz step size,

• Input power: -10 dBm to -50dBm,

• Acquisition range, up-to 1MHz.

• Demodulator

• BPSK/QPSK/8PSK,

• Symbol Rate – 10 to 250MSps in 1KSps step,

• RRC alpha : 0.05 to 0.35 in 0.05 step,

• Acquisition time < 0.5 sec,

• Synchronization threshold – Es/No <= 2.5dB

• Bit-Synchronizer

• NRZ – L/M/S, BP-L/M/S, DNRZ,

• Acquisition Range - +/0 0.1% of Symbol Rate

• Viterbi Decoding

• Standard ½ code rate (171, 133)6 ,

• Puncturing options of ½, 2/3 and 7/8,

• Option of Enable/Disable

*This presentation is the intellectual property of Logic Fruit Technologies . Any plagiarism or misuse is punishable according to Indian Laws.