Page 10 - MZBSWAP Rev 1.0 Introduction_160227

P. 10

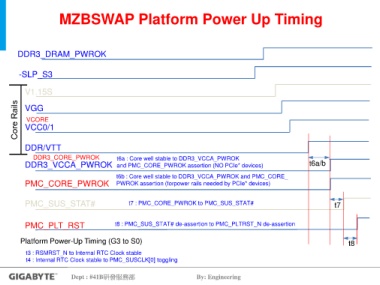

MZBSWAP Platform Power Up Timing

DDR3_DRAM_PWROK

-SLP_S3

V1.15S

VGG

VCORE

VCC0/1

DDR/VTT

DDR3_CORE_PWROK t6a : Core well stable to DDR3_VCCA_PWROK

DDR3_VCCA_PWROK and PMC_CORE_PWROK assertion (NO PCIe* devices) t6a/b

t6b : Core well stable to DDR3_VCCA_PWROK and PMC_CORE_

PMC_CORE_PWROK PWROK assertion (forpower rails needed by PCIe* devices)

PMC_SUS_STAT# t7 : PMC_CORE_PWROK to PMC_SUS_STAT# t7

PMC_PLT_RST t8 : PMC_SUS_STAT# de-assertion to PMC_PLTRST_N de-assertion

Platform Power-Up Timing (G3 to S0) t8

t3 : RSMRST_N to Internal RTC Clock stable

t4 : Internal RTC Clock stable to PMC_SUSCLK[0] toggling

Dept : #41B研發服務部 By: Engineering