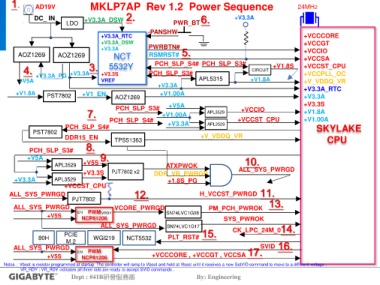

Page 3 - MKLP7AP Rev 1.2 Power Sequence _160204

P. 3

1. AD19V MKLP7AP Rev 1.2 Power Sequence 24MHz

DC_ IN +V3.3A_DSW 2. 6. +V3.3A

LDO PWR_BT

-PANSHW

+V3.3A_RTC +VCCCORE

+V3.3A_DSW +VCCGT

+V3.3A PWRBTN# +VCCIO

AOZ1269 AOZ1269 NCT RSMRST# 5. +VCCSA

4. 3. 5532Y PCH_SLP_S4# PCH_SLP_S3# CIRCUIT +V1.8S +VCCST_CPU

+V3.3A_PG +V3.3A +V3.3S PCH_SLP_S3# +VCCPLL_OC

+V5A VREF APL5315 +V1.8A +V_VDDQ_VR

+V3.3A +V3.3A_RTC

+V1.8A PST7802 +V1_EN AOZ1269 +V1.00A +V3.3A

+V5A

7. PCH_SLP_S3# +V1.00A APL3529 +VCCIO +V3.3S

+V1.8A

PCH_SLP_S4# +VCCST_CPU +V1.00A

PCH_SLP_S4# +V3.3A APL3529 SKYLAKE

PST7802

DDR15_EN TPS51363 +V_VDDQ_VR CPU

8.

PCH_SLP_S3#

+V5A 9. 10.

APL3529 +V5S ATXPWOK

+V3.3S PJT7802 x2 DDR_VR_PWRGD ALL_SYS_PWRGD

+V3.3A APL3529 +1.8S_PG

+VCCST_CPU

ALL_SYS_PWRGD 12. H_VCCST_PWRGD 11. +V1.0S

PJT7802 13.

ALL_SYS_PWRGD VCORE_PWRGD PM_PCH_PWROK

EN PWM VRDY SN74LVC1G08

+V5S

NCP81206 SYS_PWROK

ALL_SYS_PWRGD SN74LVC1G17 CK_LPC_24M_0 14.

15.

80H PCIE WGI219 NCT5532 PLT_RST#

M.2

ALL_SYS_PWRGD SVID 16.

EN PWM 17.

+V5S NCP81206 +VCCCORE , +VCCGT , VCCSA

Notes : Vboot is resistor programmed at startup. The controller will ramp to Vboot and hold at Vboot until it receives a new SetVID command to move to a different voltage ,

VR_RDY : VR_RDY indicates all three rails are ready to accept SVID commands .

Dept : #41B研發服務部 By: Engineering