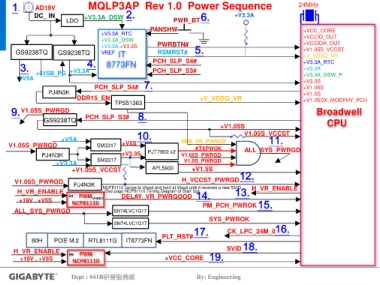

Page 2 - MQLP3AP Rev 1.0 Power Sequence _160205_Neat

P. 2

1. AD19V MQLP3AP Rev 1.0 Power Sequence 24MHz

DC_ IN +V3.3A_DSW 2. 6. +V3.3A

LDO PWR_BT

-PANSHW +VCC_CORE

+V3.3A_RTC +VCCIO_OUT

+V3.3A_DSW +VCCIOA_OUT

+V3.3A,+V3.3S PWRBTN#

GS9238TQ GS9238TQ VREF RSMRST# 5. +V1.05S_VCCST

IT

+V_VDDQ_VR

3. 4. 8773FN PCH_SLP_S4# +V3.3A_RTC

+V3.3A

+5VSB_PG +V3.3A PCH_SLP_S3# +V3.3A_DSW_P

+V5A +V3.3S

PCH_SLP_S4# 7. +V1.05S

PJ4N3K +V1.5S

DDR15_EN +V_VDDQ_VR +V1.05DX_MODPHY_PCH

TPS51363

9. 8. Broadwell

V1.05S_PWRGD

GS9238TQ PCH_SLP_S3# CPU

+V1.05S

10. V1.05S_VCCST

+V5A DDR_VR_PWRGD 11.

V1.05S_PWRGD SM3317 +V5S ATXPWOK ALL_SYS_PWRGD

PJ4N3K +V3.3S PJT7802 x2 V1.05S_PWRGD

+V3.3A SM3317 V1.5S_PWRGD

+V1.05S_VCCST APL5930 +V1.5S 12.

V1.05S_PWRGD PJ4N3K H_VCCST_PWRGD

13.

H_VR_ENABLE NCP81110 ramps to Vboot and hold at Vboot until it receives a new SVID H_VR_ENABLE

(See page NCP81110 Timing Diagram of Start Up)

EN PWM DELAY_VR_PWRGOOD 14.

+19V , +V5S NCP81110 PM_PCH_PWROK 15.

VRRDY

ALL_SYS_PWRGD SN74LVC1G17

SYS_PWROK

SN74LVC1G17 CK_LPC_24M_0 16.

PLT_RST# 17.

80H PCIE M.2 RTL8111G IT8773FN

SVID 18.

H_VR_ENABLE EN PWM

+19V , +V5S NCP81110 +VCC_CORE 19.

Dept : #41B研發服務部 By: Engineering