Page 14 - GIGABYTE Service Manual-v3.0-110101

P. 14

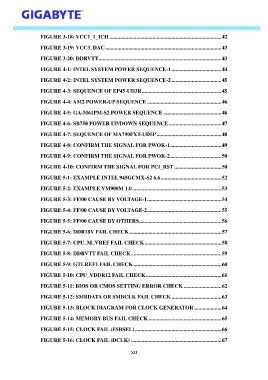

FIGURE 3-18: VCC1_1_ICH ................................................................................... 42

FIGURE 3-19: VCC3_DAC ...................................................................................... 43

FIGURE 3-20: DDRVTT........................................................................................... 43

FIGURE 4-1: INTEL SYSTEM POWER SEQUENCE-1 ..................................... 44

FIGURE 4-2: INTEL SYSTEM POWER SEQUENCE-2 ..................................... 45

FIGURE 4-3: SEQUENCE OF EP45-UD3R ........................................................... 45

FIGURE 4-4: AM2 POWER-UP SEQUENCE ....................................................... 46

FIGURE 4-5: GA-M61PM-S2 POWER SEQUENCE ........................................... 46

FIGURE 4-6: SB750 POWER UP/DOWN SEQUENCE ....................................... 47

FIGURE 4-7: SEQUENCE OF MA790FXT-UD5P ................................................ 48

FIGURE 4-8: CONFIRM THE SIGNAL FOR PWOK-1 ...................................... 49

FIGURE 4-9: CONFIRM THE SIGNAL FOR PWOK-2 ...................................... 50

FIGURE 4-10: CONFIRM THE SIGNAL FOR PCI_RST ................................... 50

FIGURE 5-1: EXAMPLE INTEL 945GCMX-S2 6.6 ............................................. 52

FIGURE 5-2: EXAMPLE VM900M 1.0 .................................................................. 53

FIGURE 5-3: FF/00 CAUSE BY VOLTAGE-1 ....................................................... 54

FIGURE 5-4: FF/00 CAUSE BY VOLTAGE-2 ....................................................... 55

FIGURE 5-5: FF/00 CAUSE BY OTHERS ............................................................. 56

FIGURE 5-6: DDR18V FAIL CHECK .................................................................... 57

FIGURE 5-7: CPU_M_VREF FAIL CHECK ......................................................... 58

FIGURE 5-8: DDRVTT FAIL CHECK ................................................................... 59

FIGURE 5-9: GTLREF1 FAIL CHECK ................................................................. 60

FIGURE 5-10: CPU_VDDR12 FAIL CHECK ........................................................ 61

FIGURE 5-11: BIOS OR CMOS SETTING ERROR CHECK ............................ 62

FIGURE 5-12: SMBDATA OR SMBCLK FAIL CHECK ..................................... 63

FIGURE 5-13: BLOCK DIAGRAM FOR CLOCK GENERATOR .................... 64

FIGURE 5-14: MEMORY BUS FAIL CHECK ...................................................... 65

FIGURE 5-15: CLOCK FAIL (FSBSEL) ................................................................ 66

FIGURE 5-16: CLOCK FAIL (DCLK) ................................................................... 67

XII