Page 26 - coba Revisi Modul Organisasi dan Arsitektur Komputer_Neat

P. 26

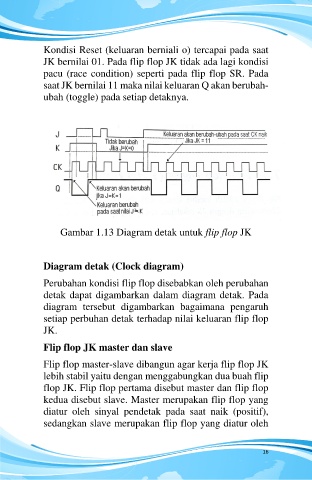

Kondisi Reset (keluaran berniali o) tercapai pada saat

JK bernilai 01. Pada flip flop JK tidak ada lagi kondisi

pacu (race condition) seperti pada flip flop SR. Pada

saat JK bernilai 11 maka nilai keluaran Q akan berubah-

ubah (toggle) pada setiap detaknya.

Gambar 1.13 Diagram detak untuk flip flop JK

Diagram detak (Clock diagram)

Perubahan kondisi flip flop disebabkan oleh perubahan

detak dapat digambarkan dalam diagram detak. Pada

diagram tersebut digambarkan bagaimana pengaruh

setiap perbuhan detak terhadap nilai keluaran flip flop

JK.

Flip flop JK master dan slave

Flip flop master-slave dibangun agar kerja flip flop JK

lebih stabil yaitu dengan menggabungkan dua buah flip

flop JK. Flip flop pertama disebut master dan flip flop

kedua disebut slave. Master merupakan flip flop yang

diatur oleh sinyal pendetak pada saat naik (positif),

sedangkan slave merupakan flip flop yang diatur oleh

16