Page 295 - Untitled

P. 295

༛

วงจรดิจิตอลละลอจิก༛ ༛ ༛บททีไ༛9༛ชิฟรีจิสตอรຏ༛༛༛279

༛ ༛ ༛ จากตารางสดงการท้างาน༛มืไออินพุต༛A༛ละ༛B༛เดຌรับลอจิก༛1༛พรຌอมกัน༛จะปຓนการจายขຌอมูล༛

1༛฿หຌกับวงจร༛ตมืไออินพุต༛A༛หรือ༛B༛เดຌรับลอจิก༛0༛ตัว฿ดตัวหนึไงหรือทัๅงสองอินพุตจะปຓนการจายลอจิก༛

0༛฿หຌกับวงจร༛ส้าหรับการควบคุม฿หຌขຌอมูลเปสดงผลทีไขา༛Serial-Out༛ตຌองท้าการจายสัญญาณพัลสຏหรือ

สัญญาณนาฬิกา฿หຌกับขา༛Clock༛จ้านวน༛8༛พัลสຏ༛

ຏ

༛ ༛ ༛ จากรูปทีไ༛9.4༛(ข)༛สดงสัญลักษณบบมาตรฐาน༛IEEE/ANSI༛ชืไอ༛SRG8༛หมายถึง༛Shift༛

Register༛ขนาด༛8༛บิต༛ครืไองหมาย༛->༛ทีไขา༛Clock༛หมายถึง༛มืไอมีการจายสัญญาณพัลสຏ฿หຌกับขานีๅ༛ขຌอมูล

จะลืไอนจากซຌายมือเปทางขวามือ༛

༛ ༛

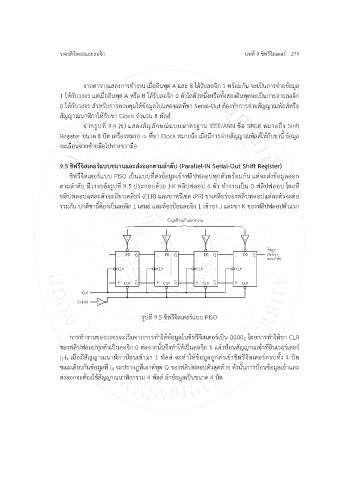

9.5༛ชิฟรีจิสตอรຏบบขนานละสงออกตามล้าดับ༛(Parallel-IN༛Serial-Out༛Shift༛Register)༛

ู

ู

ั

༛ ชิฟรีจิสตอรຏบบ༛PISO༛ปຓนบบทีไสงขຌอมลขຌาฟลิปฟลอปทุกตวพรຌอมกัน༛ตจะสงขຌอมลออก

ຌ

ี

ั

ตามล้าดบ༛มวงจรดังรูปทีไ༛9.5༛ประกอบดวย༛J-K༛ฟลิปฟลอป༛4༛ตัว༛ท้างานปຓน༛D༛ฟลิปฟลอป༛ดยทีไ༛

ั

ฟลิปฟลอปตละตวจะมขาคลียรຏ༛(CLR)༛ละขาพรีซต༛(PR)༛ขาคลียรຏของฟลิปฟลอปตละตวจะตอ

ี

ั

รวมกัน༛ปกติขานีๅตຌองปຓนลอจิก༛1༛สมอ༛ละตຌองปງอนลอจิก༛1༛ขຌาขา༛J༛ละขา༛K༛ของฟลิปฟลอปตัวรก༛

༛

I I I I

1 2 3 4

Q Q Q

I

5

༛

รูปทีไ༛9.5༛ชิฟรีจิสตอรຏบบ༛PISO༛

༛

ู

༛ การท้างานของวงจรจะริไมจากการท้า฿หຌขຌอมล฿นชิฟรีจิสตอรຏปຓน༛0000 2༛ดยการท้า฿หຌขา༛CLR༛༛

ิ

ของฟลิปฟลอปทุกตัวปຓนลอจิก༛0༛ตอจากนัๅนจึงท้า฿หຌปຓนลอจิก༛1༛ลຌวปງอนสัญญาณขຌาทีไอนวอรຏตอรຏ༛༛

I1-I4༛มืไอมสัญญาณนาฬิกาปງอนขຌามา༛1༛พลสຏ༛จะท้า฿หຌขຌอมูลถูกสงขຌาชิฟรีจิสตอรຏครบทัๅง༛4༛บิต༛

ั

ี

ขณะดียวกันขຌอมูลทีไ༛I4༛จะปรากฏทีไอาตຏพุต༛Q༛ของฟลิปฟลอปตัวสุดทຌาย༛ดังนัๅนการปງอนขຌอมูลขຌาละ

สงออกจะตຌอง฿ชຌสัญญาณนาฬิการวม༛4༛พัลสຏ༛ถຌาขຌอมูลปຓนขนาด༛4༛บิต༛

༛

༛

༛