Page 11 - MZBAYAP Rev 1.2 Introduction _160119 _Neat

P. 11

• Dual or Quad-core CPU

• Up to four IA-compatible low power Intel® processor cores

— One thread per core

• Two-wide instruction decode, out of order execution

• On-die, 32 KB 8-way L1 instruction cache and 24 KB 6-way L1 data cache per core

• On-die, 1 MB, 16-way L2 cache, shared per two cores

• 36-bit physical address, 48-bit linear address size support

• Supported C-states: C0, C1, C1E, C6C, C6, C7 for Bay Trail-M SoC (C7 is only valid

for selected SKUs), C0 and C1 for Bay Trail-D SoC

• Supports Intel Virtualization Technology (Intel VT-x)

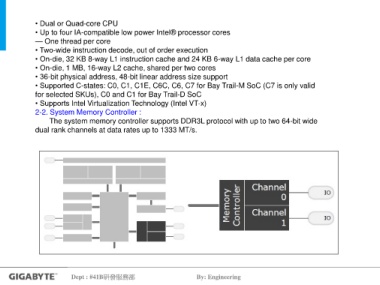

2-2. System Memory Controller :

The system memory controller supports DDR3L protocol with up to two 64-bit wide

dual rank channels at data rates up to 1333 MT/s.

Dept : #41B研發服務部 By: Engineering