Page 90 - E-MODUL ORGANISASI DAN ARSITEKTUR KOMPUTER FIX

P. 90

Berdasar tabel kebenaran di atas dapat dibaca bahwa jika masukan

SR bernilai 00 maka Kondisi Q akan tetap seperti semula, kalau

awalnya bernilai o maka akan tetap bernilai 0 dan sebaliknya. Jika

masukan SR bernilai 01, apa pun kondisi sebelumnya, Q akan

bernilai 0. Jika masukan SR bernilai 10, apa pun kondisi

sebelumnya, Q akan bernilai 1

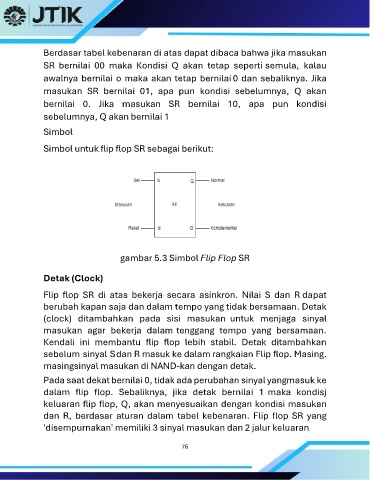

Simbol

Simbol untuk flip flop SR sebagai berikut:

gambar 5.3 Simbol Flip Flop SR

Detak (Clock)

Flip flop SR di atas bekerja secara asinkron. Nilai S dan R dapat

berubah kapan saja dan dalam tempo yang tidak bersamaan. Detak

(clock) ditambahkan pada sisi masukan untuk menjaga sinyal

masukan agar bekerja dalam tenggang tempo yang bersamaan.

Kendali ini membantu flip flop lebih stabil. Detak ditambahkan

sebelum sinyal S dan R masuk ke dalam rangkaian Flip flop. Masing.

masing sinyal masukan di NAND-kan dengan detak.

Pada saat dekat bernilai 0, tidak ada perubahan sinyal yang masuk ke

dalam flip flop. Sebaliknya, jika detak bernilai 1 maka kondisj

keluaran flip flop, Q, akan menyesuaikan dengan kondisi masukan

dan R, berdasar aturan dalam tabel kebenaran. Flip flop SR yang

'disempurnakan' memiliki 3 sinyal masukan dan 2 jalur keluaran

76