Page 92 - E-MODUL ORGANISASI DAN ARSITEKTUR KOMPUTER FIX

P. 92

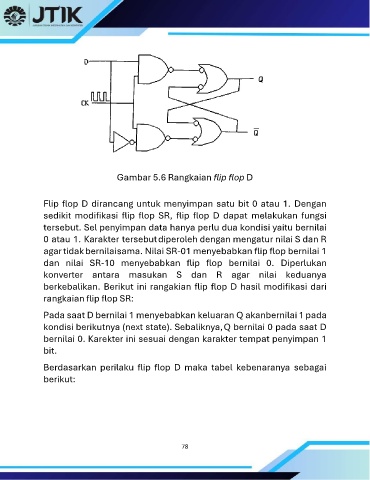

Gambar 5.6 Rangkaian flip flop D

Flip flop D dirancang untuk menyimpan satu bit 0 atau 1. Dengan

sedikit modifikasi flip flop SR, flip flop D dapat melakukan fungsi

tersebut. Sel penyimpan data hanya perlu dua kondisi yaitu bernilai

0 atau 1. Karakter tersebut diperoleh dengan mengatur nilai S dan R

agar tidak bernilai sama. Nilai SR-01 menyebabkan flip flop bernilai 1

dan nilai SR-10 menyebabkan flip flop bernilai 0. Diperlukan

konverter antara masukan S dan R agar nilai keduanya

berkebalikan. Berikut ini rangakian flip flop D hasil modifikasi dari

rangkaian flip flop SR:

Pada saat D bernilai 1 menyebabkan keluaran Q akan bernilai 1 pada

kondisi berikutnya (next state). Sebaliknya, Q bernilai 0 pada saat D

bernilai 0. Karekter ini sesuai dengan karakter tempat penyimpan 1

bit.

Berdasarkan perilaku flip flop D maka tabel kebenaranya sebagai

berikut:

78