Page 21 - Multipath MIPS

P. 21

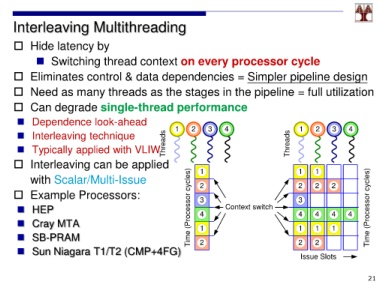

Interleaving Multithreading

Hide latency by

Switching thread context on every processor cycle

Eliminates control & data dependencies = Simpler pipeline design

Need as many threads as the stages in the pipeline = full utilization

Can degrade single-thread performance

Dependence look-ahead 1234 1234

Interleaving technique Threads

Time (Processor cycles)

Typically applied with VLIW

Threads

Interleaving can be applied Time (Processor cycles)111

2 Context switch 222

with Scalar/Multi-Issue 3 3

Example Processors: 4 444 4

1 111

HEP 2 22

Cray MTA Issue Slots

SB-PRAM

Sun Niagara T1/T2 (CMP+4FG)

21