Page 8 - Multipath MIPS

P. 8

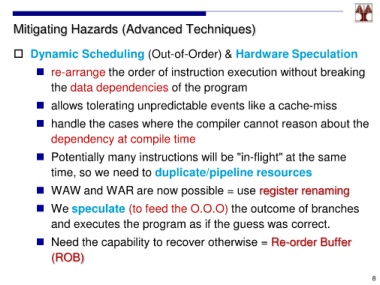

Mitigating Hazards (Advanced Techniques)

Dynamic Scheduling (Out-of-Order) & Hardware Speculation

re-arrange the order of instruction execution without breaking

the data dependencies of the program

allows tolerating unpredictable events like a cache-miss

handle the cases where the compiler cannot reason about the

dependency at compile time

Potentially many instructions will be "in-flight" at the same

time, so we need to duplicate/pipeline resources

WAW and WAR are now possible = use register renaming

We speculate (to feed the O.O.O) the outcome of branches

and executes the program as if the guess was correct.

Need the capability to recover otherwise = Re-order Buffer

(ROB)

8