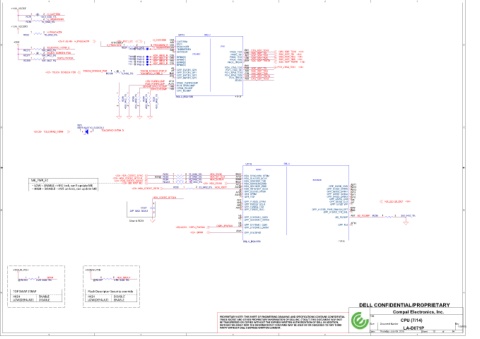

Page 12 - vinafix.com_Compal AAL15 LA-D071P r1.0

P. 12

5 4 3 2 1

+1.0V_VCCST

1 @ 2 H_CATERR#

RC79 49.9_0402_1%

1 2 H_THERMTRIP#

RC80 1K_0402_5%

+1.0V_VCCSTG

1 2 H_PROCHOT#

RC83 1K_0402_5% UC1D SKL-U

<29>

+3VS <29,41,42,48> H_PROCHOT# 8/19 DG0.9 PECI_EC H_CATERR# D63 CATERR#

A54

D H_PROCHOT# 1 2 H_PROCHOT#_R C65 PECI JTAG D

1 2 TOUCHPAD_INTR#_D RC84 499_0402_1% H_THERMTRIP# C63 PROCHOT#

RC272 10K_0402_5% T4946 @ PAD~D A65 THERMTRIP# B61 CPU_XDP_TCK0 CPU_XDP_TCK0 <14>

1 @ 2 TOUCH_SCREEN_PD# SKTOCC# PROC_TCK D60 SOC_XDP_TDI

RC277 10K_0402_5% T4942 @ PAD~D XDP_OBS0_R C55 CPU MISC PROC_TDI A61 SOC_XDP_TDO SOC_XDP_TDI <14>

SOC_XDP_TDO <14>

1 2 DGPU_PWROK XDP_OBS1_R D55 BPM#[0] PROC_TDO C60 SOC_XDP_TMS

PROC_TMS

RC360 10K_0402_5% T4941 @ PAD~D XDP_OBS2_R B54 BPM#[1] PROC_TRST# B59 SOC_XDP_TRST# SOC_XDP_TMS <14>

T10 @ PAD~D

<14>

SOC_XDP_TRST#

BPM#[2]

T11 @ PAD~D XDP_OBS3_R C56 BPM#[3] B56

A6 PCH_JTAG_TCK D59 SOC_XDP_TDI PCH_JTAG_TCK1 <14>

TOUCH_SCREEN_PD# 1 @ 2 TOUCH_SCREEN_PD#_R A7 GPP_E3/CPU_GP0 PCH_JTAG_TDI A56 SOC_XDP_TDO

<32> TOUCH_SCREEN_PD# BA5 GPP_E7/CPU_GP1 PCH_JTAG_TDO C59

RC394 0_0402_5% TOUCHPAD_INTR#_D SOC_XDP_TMS

AY5 GPP_B3/CPU_GP2 PCH_JTAG_TMS C61 SOC_XDP_TRST#

GPP_B4/CPU_GP3 PCH_TRST# A59 CPU_XDP_TCK0

CPU_POPIRCOMP AT16 JTAGX

PCH_POPIRCOMP AU16 PROC_POPIRCOMP

EDRAM_OPIO_RCOMP H66 PCH_OPIRCOMP

EOPIO_RCOMP H65 OPCE_RCOMP

OPC_RCOMP

1 1 1 1

RC88 49.9_0402_1% RC89 49.9_0402_1% RC90 49.9_0402_1% RC91 49.9_0402_1% SKL-U_BGA1356 4 OF 20

2 2 2 2

DZ3

C RB751S40T1G_SOD523-2 C

<29,38> TOUCHPAD_INTR# 1 2 TOUCHPAD_INTR#_D

UC1G SKL-U

AUDIO

RC92 1 2 33_0402_5% HDA_SYNC BA22

<23> HDA_CODEC_SYNC EMI@ RC93 1 2 33_0402_5% HDA_BIT_CLK AY22 HDA_SYNC/I2S0_SFRM

<23> HDA_CODEC_BITCLK 1 2 BB22 HDA_BLK/I2S0_SCLK

ME_FWP_EC <23> HDA_CODEC_SDOUT RC94 33_0402_5% HDA_SDOUT HDA_SDO/I2S0_TXD SDIO/SDXC

<29> ME_FWP_EC RC223 1 2 1K_0402_5% <23> HDA_SDIN0 BA21 HDA_SDI0/I2S0_RXD

AY21

‧ LOW = ENABLE -->ME lock, can't update ME RC95 1 2 33_0402_5% HDA_RST# AW22 HDA_SDI1/I2S1_RXD GPP_G0/SD_CMD AB11

AB13

‧ HIGH = DISABLE -->ME un-lock, can update ME <23> HDA_CODEC_RST# J5 HDA_RST#/I2S1_SCLK GPP_G1/SD_DATA0 AB12

AY20 GPP_D23/I2S_MCLK GPP_G2/SD_DATA1 W12

AW20 I2S1_SFRM GPP_G3/SD_DATA2 W11

HDA_CODEC_BITCLK I2S1_TXD GPP_G4/SD_DATA3 W10

AK7 GPP_G5/SD_CD# W8 KB_LED_BL_DET <38>

1 AK6 GPP_F1/I2S2_SFRM GPP_G6/SD_CLK W7

GPP_F0/I2S2_SCLK

GPP_G7/SD_WP

AK9

CC27 AK10 GPP_F2/I2S2_TXD BA9

B 22P_0402_50V8J 2 GPP_F3/I2S2_RXD GPP_A17/SD_PWR_EN#/ISH_GP7 BB9 B

GPP_A16/SD_1P8_SEL

H5 AB7 SD_RCOMP RC96 1 2 200_0402_1%

D7 GPP_D19/DMIC_CLK0 SD_RCOMP

Close to RC93 GPP_D20/DMIC_DATA0

D8 AF13

DGPU_PWROK C8 GPP_D17/DMIC_CLK1 GPP_F23

<29,40,52> DGPU_PWROK GPP_D18/DMIC_DATA1

AW5

<23> SPKR GPP_B14/SPKR

SKL-U_BGA1356 7 OF 20

+3VALW_PCH +3VALW_PCH

1 2 SPKR 1 2 HDA_SDOUT

@ RC183 8.2K_0402_5% @ RC187 4.7K_0402_5%

TOP SWAP STRAP Flash Descriptor Security override

A A

HIGH ENABLE HIGH DISABLE

LOW(DEFAULT) DISABLE LOW(DEFAULT) ENABLE

DELL CONFIDENTIAL/PROPRIETARY

Co

Co

Compal Electronics, Inc.mpal Electronics, Inc.mpal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL Ti Ti Titletletle

CP

CP

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT CPU (7/14)U (7/14)U (7/14)

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION, Si Si Sizezeze Do Re Re Revvv

Document Numbercument Numbercument Number

Do

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD 1.0(A00)0(A00)0(A00)

1. 1.

LA-D071P-D071P-D071P

LA

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT. LA

64

12

12

64

Sh

Date:te:te:

Da Th Th Thursday, July 09, 2015ursday, July 09, 2015ursday, July 09, 2015 Sh 12 of of of 64

Sheeteeteet

Da

5 4 3 2 1