Page 63 - Mechatronics with Experiments

P. 63

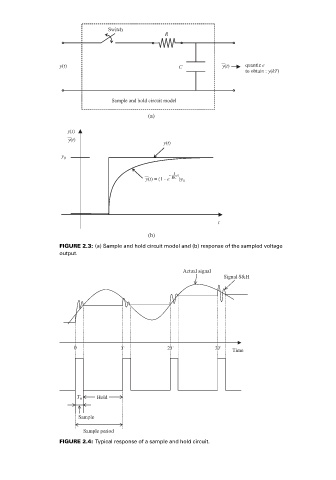

Switch

R

y(t) C y(t) quantiz e

to obtain : y(kT)

Sample and hold circuit model

(a)

y(t)

y(t)

y(t)

y

0

- 1 t

y(t) = (1 - e RC )y 0

t

(b)

FIGURE 2.3: (a) Sample and hold circuit model and (b) response of the sampled voltage

output.

Actual signal

Signal S&H

0 T 2T 3T Time

T 0 Hold

Sample

Sample period

FIGURE 2.4: Typical response of a sample and hold circuit.