Page 56 - Data Science Algorithms in a Week

P. 56

40 Edwin Cortes, Luis Rabelo and Gene Lee

14. STD processor Speed: It is the standard deviation of the speed of the CPUs

used in the simulation.

15. Mean RAM: It is the mean of the RAM memory used by the CPUs in the

system.

16. STD RAM: It is the standard deviation of the RAM memory used by the

CPUs in the system.

17. Critical Path%: It is the Critical Path taking into consideration the

sequential estimated processing time.

18. Theoretical Speedup: It is the theoretical (maximum) speedup to be

achieved with perfect parallelism in the simulation.

19. Local Events/(Local Events + External Events): It is the ratio of the total

local events divided by the summation of the total local events and the total

external events during a specific unit of Simulation Time (estimated).

20. Subscribers/(Publishers + Subscribers): It is the ratio of the total number

of objects subscribing to a particular object divided by the summation of the

total number of publishers and subscribers.

21. Block or Scatter?: Block and scatter are decomposition algorithms being

used to distribute the simulation objects in the parallel/distributed system - If

Block is being selected then this value is 1. and if Scatter is selected then this

value is 0.

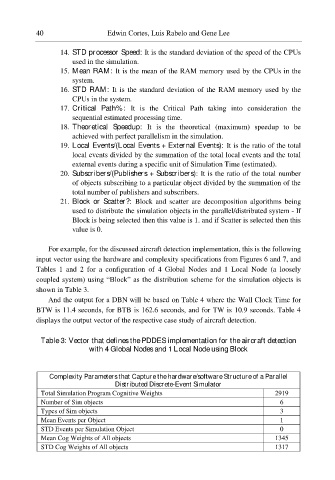

For example, for the discussed aircraft detection implementation, this is the following

input vector using the hardware and complexity specifications from Figures 6 and 7, and

Tables 1 and 2 for a configuration of 4 Global Nodes and 1 Local Node (a loosely

coupled system) using “Block” as the distribution scheme for the simulation objects is

shown in Table 3.

And the output for a DBN will be based on Table 4 where the Wall Clock Time for

BTW is 11.4 seconds, for BTB is 162.6 seconds, and for TW is 10.9 seconds. Table 4

displays the output vector of the respective case study of aircraft detection.

Table 3: Vector that defines the PDDES implementation for the aircraft detection

with 4 Global Nodes and 1 Local Node using Block

Complexity Parameters that Capture the hardware/software Structure of a Parallel

Distributed Discrete-Event Simulator

Total Simulation Program Cognitive Weights 2919

Number of Sim objects 6

Types of Sim objects 3

Mean Events per Object 1

STD Events per Simulation Object 0

Mean Cog Weights of All objects 1345

STD Cog Weights of All objects 1317