Page 302 - FUNDAMENTALS OF COMPUTER

P. 302

302 Fundamentals of Computers NPP

This is also a binary gate whose numbers `h ^r EH$ Eogm JoQ> h¡ {Og_| H$_ go H$_ Xmo BZnwQ>

of inputs must be greater than or equal to two.

The output of XOR gate can also be written in hmoVo h¢Ÿ& BgH$m AmCQ>nwQ> POS (Product of Sum) Ho$

POS (product of Sum) form as: ê$n _| ^r {bIm Om gH$Vm h¡ …

(A+ B ) (A. + B )

A

B Y = (A+B) . (A+B)

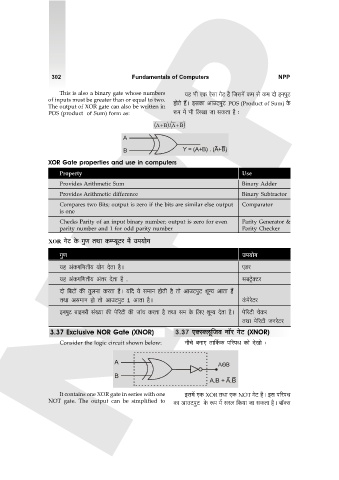

XOR Gate properties and use in computers

Property Use

Provides Arithmetic Sum Binary Adder

Provides Arithmetic difference Binary Subtractor

Compares two Bits; output is zero if the bits are similar else output Comparator

is one NPP

Checks Parity of an input binary number; output is zero for even Parity Generator &

parity number and 1 for odd parity number Parity Checker

XOR JoQ> Ho$ JwU VWm H$åß`yQ>a _o§ Cn`moJ

JwU Cn`moJ

`h A§H$J{UVr` `moJ XoVm h¡Ÿ& ES>a

`h A§H$J{UVr` A§Va XoVm h¡ . g~Q´>oŠQ>a

Xmo {~Q>m| H$s VwbZm H$aVm h¡Ÿ& `{X `o g_mZ hmoVr h¡ Vmo AmCQ>nwQ> eyÝ` AmVm h¢

VWm Ag_mZ hmo Vmo AmCQ>nwQ> 1 AmVm h¡Ÿ& H§$noaoQ>a

BZnwQ> ~mBZar g§»`m H$s no[aQ>r H$s Om§M H$aVm h¡ VWm g_ Ho$ {bE eyÝ` XoVm h¡Ÿ& no[aQ>r MoH$a

VWm no[aQ>r OZaoQ>a

3.37 Exclusive NOR Gate (XNOR) 3.37 EŠñŠcy{Od Zm°a JoQ> (XNOR)

Consider the logic circuit shown below: ZrMo ~ZmE Vm{H©$H$ n[anW H$mo XoImo …

A AOB

B

A.B + A.B

It contains one XOR gate in series with one Bg_| EH$ XOR VWm EH$ NOT JoQ> h¡Ÿ& Bg n[anW

NOT gate. The output can be simplified to H$m AmCQ>nwQ> Ho$ ê$n _| gab {H$`m Om gH$Vm h¡Ÿ& ~m°Šg