Page 244 - Mechatronics with Experiments

P. 244

230 MECHATRONICS

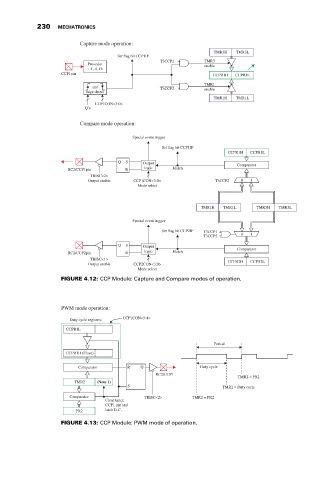

Capture mode operation:

TMR3H TMR3L

Set flag bit CCP1IF

T3CCP2 TMR3

Prescaler enable

÷ 1, 4, 16

CCP1pin CCPR1H CCPR1L

TMR1

and T3CCP2 enable

edge detect

TMR1H TMR1L

CCP1CON<3:0>

Q’s

Compare mode operation:

Special event trigger

Set flag bit CCP1IF

CCPR1H CCPR1L

Q S Output

logic Match Comparator

RC2/CCP1pin R

TRISC<2>

Output enable CCP1CON<3:0> T3CCP2 0 1

Mode select

TMR1H TMR1L TMR3H TMR3L

Special event trigger

Set flag bit CCP2IF T3CCP1

T3CCP2 0 1

Q S Output

logic Match Comparator

RC2/CCP2pin R

TRISC<1>

Output enable CCP2CON<3:0> CCPR2H CCPR2L

Mode select

FIGURE 4.12: CCP Module: Capture and Compare modes of operation.

PWM mode operation:

CCP1CON<5:4>

Duty cycle registers

CCPR1L

Period

CCPR1H (Slave)

Comparator R Q Duty cycle

RC2/CCP1

TMR2 = PR2

TMR2 (Note 1)

S TMR2 = Duty cycle

Comparator TRISC<2> TMR2 = PR2

Clear timer,

CCP1 pin and

PR2 latch D.C.

FIGURE 4.13: CCP Module: PWM mode of operation.