Page 245 - Mechatronics with Experiments

P. 245

MICROCONTROLLERS 231

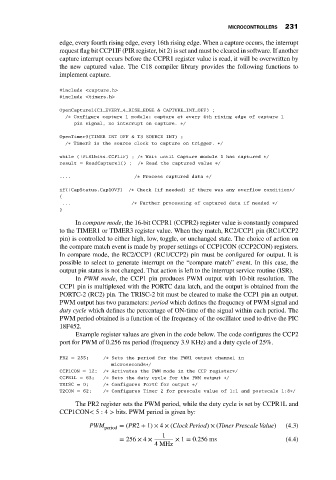

edge, every fourth rising edge, every 16th rising edge. When a capture occurs, the interrupt

request flag bit CCP1IF (PIR register, bit 2) is set and must be cleared in software. If another

capture interrupt occurs before the CCPR1 register value is read, it will be overwritten by

the new captured value. The C18 compiler library provides the following functions to

implement capture.

#include <capture.h>

#include <timers.h>

OpenCapture1(C1_EVERY_4_RISE_EDGE & CAPTURE_INT_OFF) ;

/∗ Configure capture 1 module: capture at every 4th rising edge of capture 1

pin signal, no interrupt on capture. ∗/

OpenTimer3(TIMER_INT_OFF & T3_SOURCE_INT) ;

/∗ Timer3 is the source clock to capture on trigger. ∗/

while (!PIR1bits.CCP1IF) ; /∗ Wait until Capture module 1 has captured ∗/

result = ReadCapture1() ; /∗ Read the captured value ∗/

.... /∗ Process captured data ∗/

if(!CapStatus.Cap1OVF) /∗ Check (if needed) if there was any overflow condition∗/

{

... /∗ Further processing of captured data if needed ∗/

}

In compare mode, the 16-bit CCPR1 (CCPR2) register value is constantly compared

to the TIMER1 or TIMER3 register value. When they match, RC2/CCP1 pin (RC1/CCP2

pin) is controlled to either high, low, toggle, or unchanged state. The choice of action on

the compare match event is made by proper settings of CCP1CON (CCP2CON) registers.

In compare mode, the RC2/CCP1 (RC1/CCP2) pin must be configured for output. It is

possible to select to generate interrupt on the “compare match” event. In this case, the

output pin status is not changed. That action is left to the interrupt service routine (ISR).

In PWM mode, the CCP1 pin produces PWM output with 10-bit resolution. The

CCP1 pin is multiplexed with the PORTC data latch, and the output is obtained from the

PORTC-2 (RC2) pin. The TRISC-2 bit must be cleared to make the CCP1 pin an output.

PWM output has two parameters: period which defines the frequency of PWM signal and

duty cycle which defines the percentage of ON-time of the signal within each period. The

PWM period obtained is a function of the frequency of the oscillator used to drive the PIC

18F452.

Example register values are given in the code below. The code configures the CCP2

port for PWM of 0.256 ms period (frequency 3.9 KHz) and a duty cycle of 25%.

PR2 = 255; /∗ Sets the period for the PWM1 output channel in

microseconds∗/

CCP1CON = 12; /∗ Activates the PWM mode in the CCP register∗/

CCPR1L = 63; /∗ Sets the duty cycle for the PWM output ∗/

TRISC = 0; /∗ Configures PortC for output ∗/

T2CON = 62; /∗ Configures Timer 2 for prescale value of 1:1 and postscale 1:8∗/

The PR2 register sets the PWM period, while the duty cycle is set by CCPR1L and

CCP1CON< 5:4 > bits. PWM period is given by:

PWM = (PR2 + 1) × 4 × (Clock Period) × (Timer Prescale Value) (4.3)

period

1

= 256 × 4 × × 1 = 0.256 ms (4.4)

4MHz