Page 252 - Mechatronics with Experiments

P. 252

238 MECHATRONICS

2. PORTB pins 4, 5, 6, 7 can be programmed to generate interrupt on change-of-state

(on rising edge or falling edge). PORTB pins 4–7 change-of-state interrupts can be

enabled or disabled as well as priority set as a group under program control.

3. “ADC conversion done” is another interrupt, which is generated when an ADC

conversion is completed. When ADC conversion complete interrupt is generated

(assuming it is enabled), PIR1-bit 6 is set. The logic to trigger the start of the ADC

conversion must be handled separately (i.e., after reading the current ADC conversion

at the ISR routine, or periodically performing ADC conversion based on a TIMER

generated signal).

4. TIMER interrupts (interrupt-on-overflow generated by TIMER0, TIMER1, TIMER3,

and when TIMER2 data register = PR2 register). When timer interrupts are enabled

and timer overflow occurs, resulting in interrupt generation, interrupt status flag bits

in corresponding registers associated with the interrupt source are set that can be

used in the ISR routine to determine the source of the interrupt (INTCON bit 1

for TIMER0, PIR1-bit 0 for TIMER1, PIR1-bit 1 for TIMER2, and PIR2-bit 1 for

TIMER3).

5. CCP1, CCP2 interrupts (once enabled and priorities are selected to be either as high or

low) are generated as folows: in capture mode, a TIMER1 register capture occurred,

and in compare mode a TIMER1 register match occurred.

6. Communication peripheral interrupts (master synchronous serial port, addressable

USART, parallel slave port, EEPROM write interrupt).

For external interrupts at INT0-INT2 (RB0-RB2) pins or PORTB pins 4–7 (RB3-RB7) input

change interrupt, expected interrupt latency time is three to four instruction cycles. Notice

that PIC 18F452 groups all interrupts into two categories and provides two ISR addresses:

a low priority group with ISR address stored at 000018h, and a high priority group with ISR

address stored at 000008h. Within each group, application software must be implemented

by testing interrupt flag bits (bits contained in the 10 registered listed above) to determine

which one of the interrupt sources in a high or low priority group has triggered the interrupt.

The RESET signal can be considered as a non-maskable interrupt. The address for

the program code to execute on the RESET signal is stored at the vector address 0000h.

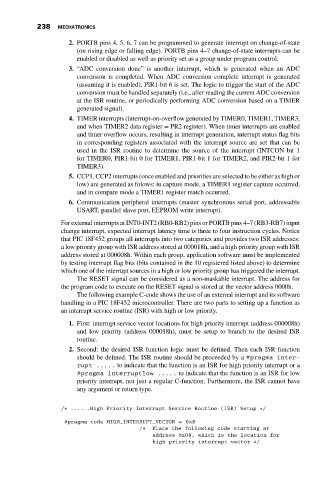

The following example C-code shows the use of an external interrupt and its software

handling in a PIC 18F452 microcontroller. There are two parts to setting up a function as

an interrupt service routine (ISR) with high or low priority.

1. First: interrupt service vector locations for high priority interrupt (address 000008h)

and low priority (address 000018h), must be setup to branch to the desired ISR

routine.

2. Second: the desired ISR function logic must be defined. Then each ISR function

should be defined. The ISR routine should be proceeded by a #pragma inter-

rupt ..... to indicate that the function is an ISR for high priority interrupt or a

#pragma interruptlow ..... to indicate that the function is an ISR for low

priority interrupt, not just a regular C-function. Furthermore, the ISR cannot have

any argument or return type.

/∗ ......High Priority Interrupt Service Routine (ISR) Setup ∗/

#pragma code HIGH_INTERRUPT_VECTOR = 0x8

/∗ Place the following code starting at

address 0x08, which is the location for

high priority interrupt vector ∗/