Page 138 - E-Modul PRE

P. 138

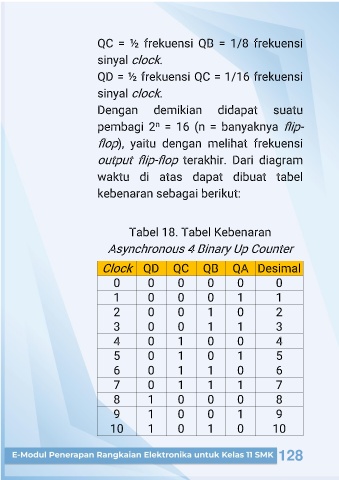

QC = ½ frekuensi QB = 1/8 frekuensi

sinyal clock

.

QD = ½ frekuensi QC = 1/16 frekuensi

.

sinyal clock

Dengan demikian didapat suatu

pembagi 2 = 16 (n = banyaknya flip-

n

flop), yaitu dengan melihat frekuensi

output flip-flop terakhir. Dari diagram

waktu di atas dapat dibuat tabel

kebenaran sebagai berikut:

Tabel 18. Tabel Kebenaran

Asynchronous 4 Binary Up Counter

Clock QD QC QB QA Desimal

0 0 0 0 0 0

1 0 0 0 1 1

2 0 0 1 0 2

3 0 0 1 1 3

4 0 1 0 0 4

5 0 1 0 1 5

6 0 1 1 0 6

7 0 1 1 1 7

8 1 0 0 0 8

9 1 0 0 1 9

10 1 0 1 0 10

128

122