Page 250 - FUNDAMENTALS OF COMPUTER

P. 250

NPP

250 Fundamentals of Computers NPP

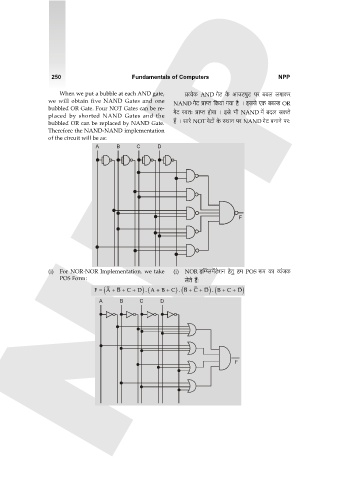

When we put a bubble at each AND gate, àË`oH$ AND JoQ> Ho$ AmCQ>nwQ> na ~~b bJmH$a

we will obtain five NAND Gates and one NAND JoQ> àmßV {H$`m J`m h¡ Ÿ& Bggo EH$ ~~ëS> OR

bubbled OR Gate. Four NOT Gates can be re-

placed by shorted NAND Gates and the JoQ> ñdV… àmßV hmoJm Ÿ& Bgo ^r NAND _| ~Xb gH$Vo

bubbled OR can be replaced by NAND Gate. h¢ Ÿ& gmao NOT JoQ>m| Ho$ ñWmZ na NAND JoQ> ~ZmZo na:

Therefore the NAND-NAND implementation

of the circuit will be as:

A B C D

F

(i) For NOR-NOR Implementation. we take (i) NOR Bpåßb_|Q>oeZ hoVw h_ POS ê$n H$m ì`§OH$

POS Form: boVo h¢:

F = (A + B + C + D ) ( . A + B + C ) ( . B + C + D ) ( . B + C + D )

A B C D

F