Page 12 - Organisasi Memori

P. 12

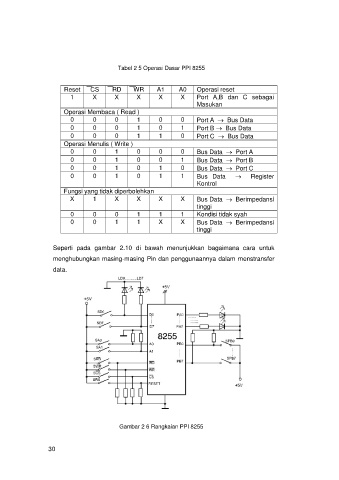

Tabel 2 5 Operasi Dasar PPI 8255

Reset CS RD WR A1 A0 Operasi reset

1 X X X X X Port A,B dan C sebagai

Masukan

Operasi Membaca ( Read )

0 0 0 1 0 0 Port A Bus Data

0 0 0 1 0 1 Port B Bus Data

0 0 0 1 1 0 Port C Bus Data

Operasi Menulis ( Write )

0 0 1 0 0 0 Bus Data Port A

0 0 1 0 0 1 Bus Data Port B

0 0 1 0 1 0 Bus Data Port C

0 0 1 0 1 1 Bus Data Register

Kontrol

Fungsi yang tidak diperbolehkan

X 1 X X X X Bus Data Berimpedansi

tinggi

0 0 0 1 1 1 Kondisi tidak syah

0 0 1 1 X X Bus Data Berimpedansi

tinggi

Seperti pada gambar 2.10 di bawah menunjukkan bagaimana cara untuk

menghubungkan masing-masing Pin dan penggunaannya dalam menstransfer

data.

Gambar 2 6 Rangkaian PPI 8255

30